眾核處理器:原理、設計與優化 | 美妙體態瑜珈在你家 - 2024年7月

眾核處理器:原理、設計與優化

本書著重介紹眾核處理器,重點關注架構優化、存儲優化、運算資源優化、通信優化以及能耗與溫度優化等方面的關鍵技術。

從計算、存儲、通信三方面介紹眾核處理器架構的設計與優化技術,基於存儲機制、存儲層次結構、共用和私有Cache以及片上網路通信機制等多方面詳細介紹瓷片眾核處理器架構,並提供瓷片眾核處理器架構的優化方案。

李兆麟,清華大學長聘教授,從事異構多核/眾核處理器、智慧處理器、並行程式設計等領域研究,主持“核高基”重大專項、重點研發計畫、自然科學基金等多個專案,在IEEE期刊與國際會議發表論文100多篇,出版教材2部。

王明羽,清華大學博士,中山大學助理教授,碩士生導師,從事多核/眾核處理器、人工智慧等領域研究,主持中國博士後科學基金,參與“核高基”重大專項等多個項目,發表學術論文10餘篇。

魏少軍,清華大學長聘教授,中國電子學會會士,IEEE Fellow,國家積體電路產業發展諮詢委員會委員,“核高基”國家科技重大專項技術總師,中國半導體行業協會副理事長,積體電路設計分會理事長,從事超大型積體電路設計方法學、數位系統高層次綜合、嵌入式系統、可重構計算晶片等領域研究,發表論文□00多篇,出版專著5部。

第1章緒論

1.1處理器發展概述

1.2眾核處理器簡介

1.3指令調度技術

1.4片上網路通信技術

1.5能耗優化技術

1.6小結

參考文獻

第2章眾核處理器架構

2.1處理器架構概述

2.2瓷片眾核處理器架構

2.3存儲機制

2.3.1存儲層次結構

2.3.2共用Cache架構

2.3.3私有Cache架構

2.4互連網路

2.4.1片上網路通信機制

2.4.2片上網路延時優化技術

2.5小結

參考文獻

第3章眾核處理器存儲優化

3.1存儲層次結構

3.2Cache優化技術

3.3存儲結構優化設計

3.3.1自我調整共用Cache結構

3.3.2自我調整私有Cache架構

3.4互連網路與Cache協同設計

3.4.1片上網路延時優化設計

3.4.2片上網路與自我調整Cache的協同設計

3.5小結

參考文獻

第4章處理器核運算資源優化

4.1流處理器

4.2流程式的核心映射和調度

4.3運算資源利用率優化技術

4.3.1同構多執行緒與核心聯合

4.3.2運算單元高利用率調度

4.4利用率感知的核心映射和調度技術

4.4.1眾核流處理架構建模

4.4.2核心映射與調度優化

4.5小結

參考文獻

第5章基於片上網路的通信優化

5.1片上網路混合策略

5.2片上網路延時和能耗建模

5.3片上網路延時優化技術

5.3.1虛擬電路交換片上網路路由器

5.3.2混合虛擬電路路徑分配演算法

5.4片上網路眾核編譯框架協同設計

5.4.1眾核編譯框架總體設計

5.4.2可執行代碼編譯生成

5.5小結

參考文獻

第6章處理器能耗與溫度優化

6.1能耗與溫度優化原理

6.2處理核能耗與溫度建模

6.3處理核指令編譯

6.3.1漏電功耗優化調度

6.3.2溫度優化的負載均衡

6.4眾核任務調度優化技術

6.4.1多工子圖劃分和子網分配

6.4.2啟發式子任務映射

6.5小結

參考文獻

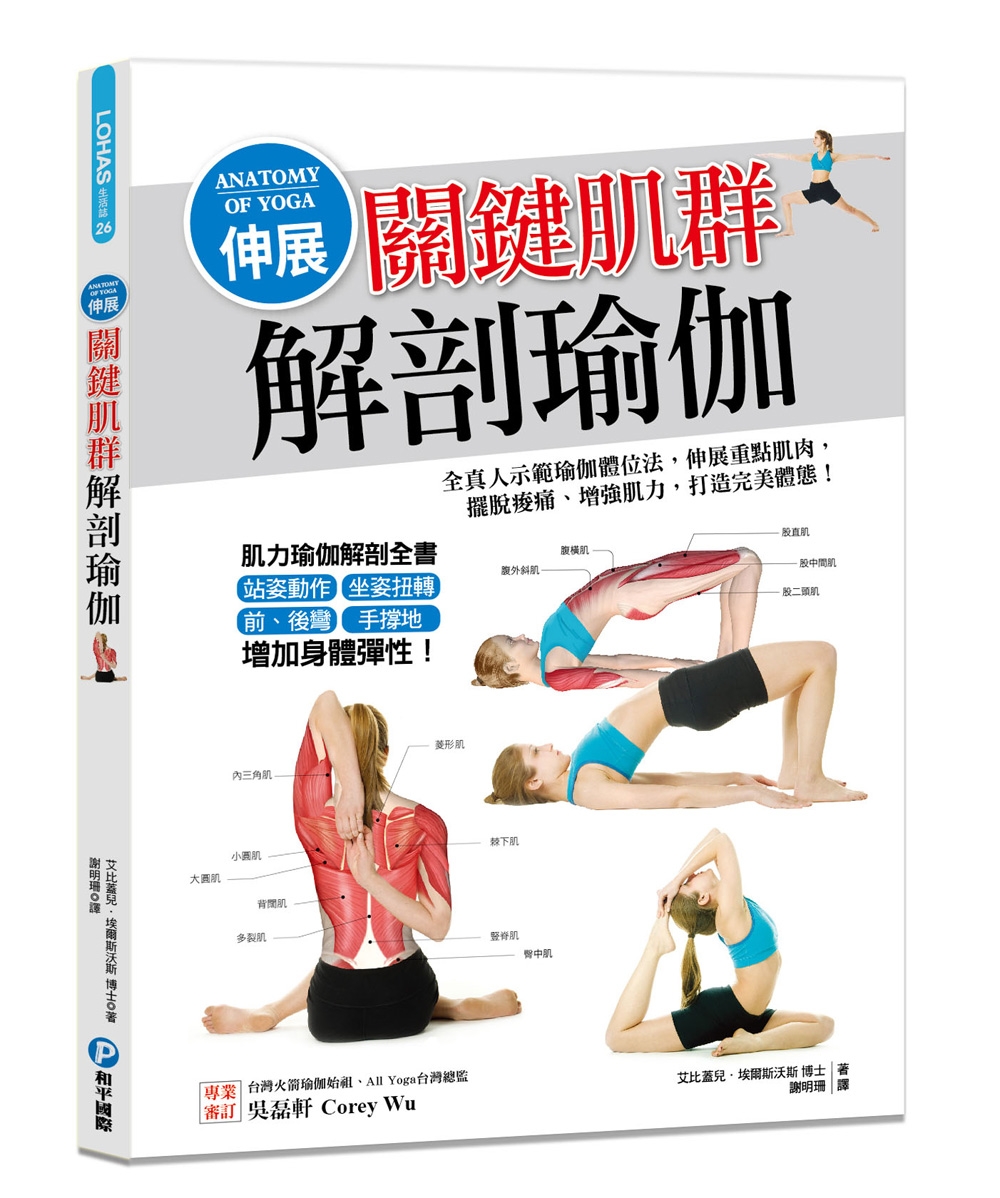

伸展關鍵肌群解剖瑜伽!:全真人示範...

伸展關鍵肌群解剖瑜伽!:全真人示範... 安寧伴行

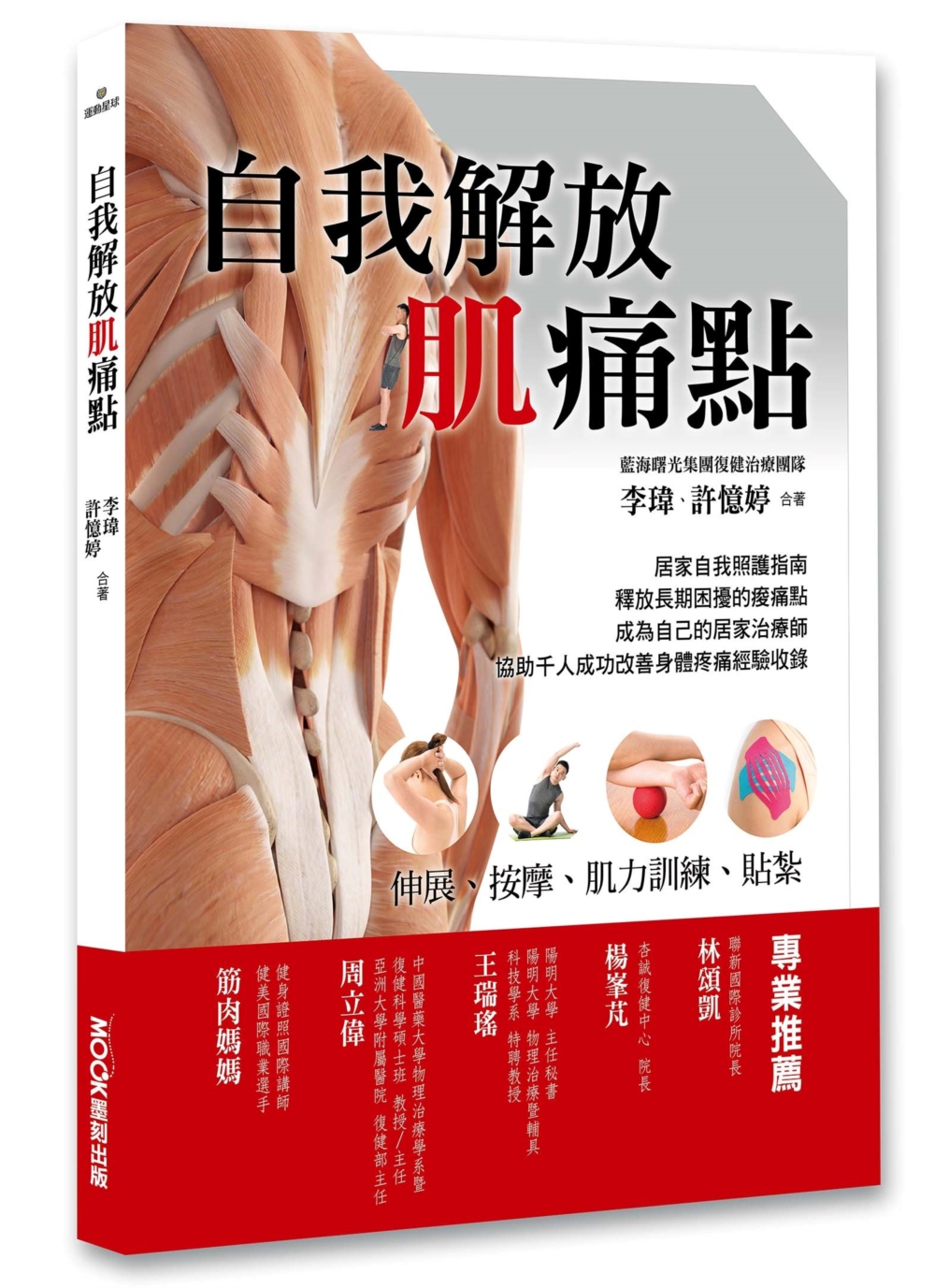

安寧伴行 自我解放肌痛點:痠痛檢測、伸展、按...

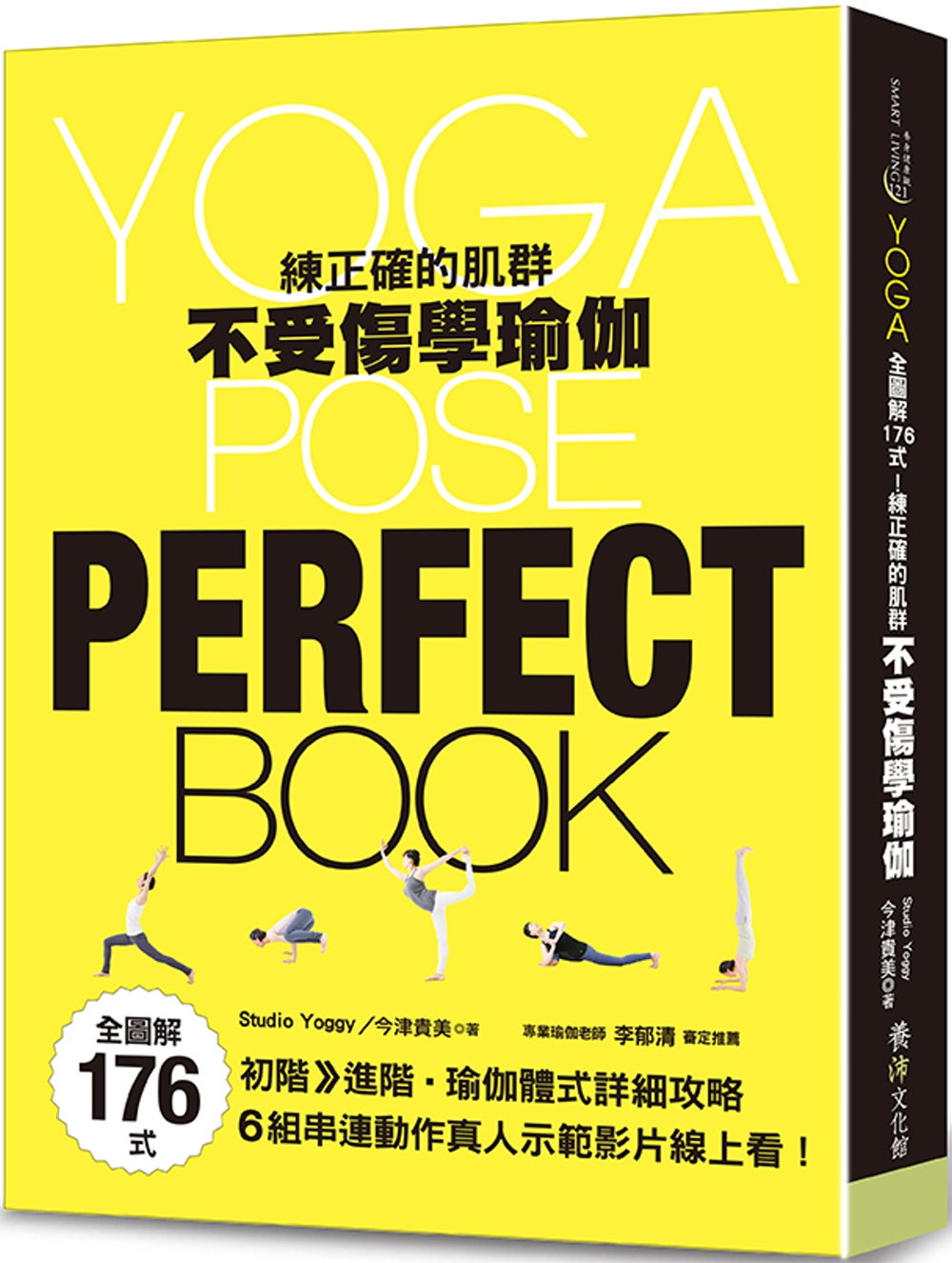

自我解放肌痛點:痠痛檢測、伸展、按... 全圖解176式!練正確的肌群‧不受...

全圖解176式!練正確的肌群‧不受... 筋膜系統伸展全書:日本筋膜伸展博士...

筋膜系統伸展全書:日本筋膜伸展博士... 滾筒瑜伽舒筋瘦身全書:訓練核心肌群...

滾筒瑜伽舒筋瘦身全書:訓練核心肌群... 經絡導引:融合中醫、易筋經、八段錦...

經絡導引:融合中醫、易筋經、八段錦... 腰痠背痛的人一定要會的跟腱按摩伸展...

腰痠背痛的人一定要會的跟腱按摩伸展... 【全圖解】醫學博士才知道的「痠痛拉...

【全圖解】醫學博士才知道的「痠痛拉...